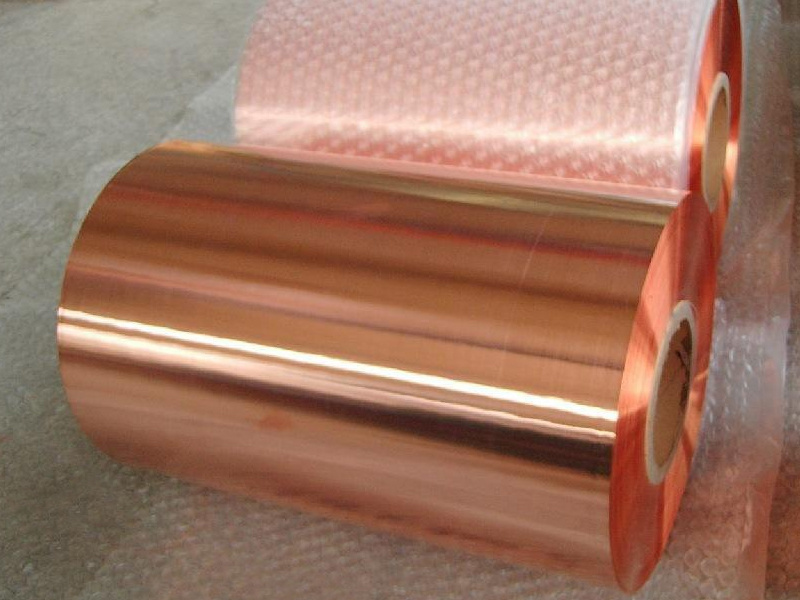

RTF 반전 동박은 회로 손실을 개선할 수 있습니다

2022-10-10

RTF 반전 동박은 회로 손실을 개선할 수 있다

PCB의 전송선 손실은 주로 유전 손실과 도체 손실로 구성된다. 기존 FR4 재료에 비해 1GHz는 유전 손실과 도체 손실의 분기점이며, 1GHz 미만에서는 도체 손실이 주요 영향 요소이다. 주파수가 1GHz를 초과하면 유전 손실이 주요 요소가 된다. 그러나 매우 낮은 손실 재료의 경우 유전 손실이 더 이상 주요 손실이 아니다. 10GHz 주파수에서 도선 손실은 전송선 총 손실의 약 60%를 차지한다. 그림 4는 Lianmao IT-968 재료를 기반으로 시뮬레이션 계산한 마이크로스트립 라인과 스트립 라인의 도체 손실(전도 손실)과 유전 손실(유전 손실)을 보여준다. 스트립 라인의 이론적 손실과 실측 손실이 거의 일치하는 것을 알 수 있다. 마이크로스트립 라인이든 스트립 라인이든 유전 손실은 도체 손실보다 훨씬 작다.

비록 RTF 반전 동박 표면은 비교적 매끄럽지만, 기존 PCB 공정으로 인해 동박 표면 거칠기가 증가하여 RTF 반전 동박의 효과에 영향을 미친다. 내선 생산 공정에 따라 내층은 건막 예비 처리 및 갈변 처리를 거쳐야 한다. 이러한 두 가지 공정 처리 후 RTF 반전 동박 표면 거칠기 Rz는 원래 1.5μm에서 약 3μm로 증가한다. 이 문제를 해결하기 위해 시장에서는 저 거칠기 공정이 출시되었다. 기존 갈변제와 달리 이 공정은 RTF 반전 동박 표면을 미세 에칭하지 않고 동박 표면을 세척한 후 주석층을 증착하고 실록산으로 표면을 개질하여 PP 압착 시 브리징 역할을 하여 동박과 PP의 결합력을 어느 정도 높일 수 있다.

채택 RTF 반전 동박 공정과 기존 갈변 공정 후 RTF 반전 동박 표면 거칠기 비교는 표 1에 나와 있다. 그림에서 알 수 있듯이 기존 건막 예비 처리 및 갈변 공정은 모두 동박 표면 거칠기를 어느 정도 높일 수 있다. 저 거칠기 공정을 채택한 후 동박 표면 거칠기는 원래 동박과 거의 동일하다. 시험 결과 저 거칠기 공정을 채택한 후 신호 손실은 0.03~0.05db/Inch(12.5GHz) 감소할 수 있다. 객관적으로 볼 때 초저손실 재료의 개선 폭은 그다지 크지 않다. 개선 효과와 비용 투입을 고려할 때 이 공정의 가성비는 만족스럽지 않아 널리 사용되지 않고 있다. 또한 HVLP 동의 경우 자체 거칠기로 인해 이 공정으로는 이러한 효과만 얻을 수 있다. 미래의 초저손실 재료의 경우 이러한 개선이 더욱 두드러질 것이며, NP 동박이 상용화되면 이 공정이 더욱 효과적일 것으로 예상된다.

바로 이러한 좋은 특성들 때문에 현재 대부분의 PCB 기판은 이러한 동박을 사용하고 있으며, 손실 문제를 효율적으로 해결할 수 있을 뿐만 아니라 전체 작동 속도를 높이고 전체 전기로 전송이 원활하게 이루어지도록 할 수 있다.

이전 페이지

이전 페이지:

추천 뉴스

전문 전자동박 제조업체는 전자동박의 순도를 어떻게 관리하고 시험할까요?

2024-09-24

생산된 전자동박의 주요 성능 지표는 인장강도, 신율, 전도도, 내열성 등입니다.

2024-09-04

전문 전자 동박 제조업체는 동박 제품의 안정성과 일관성을 어떻게 보장할까요?

2024-08-08

전문 전해 동박 공급업체 제품의 적용 분야는 무엇입니까?

2024-07-24

전해 동박의 결정 방향이 그 특성에 미치는 중요한 영향은 무엇입니까?

2024-07-09